본 글은 책 "혼자 공부하는 컴퓨터 구조+운영체제" 의 Chapter 5를 읽고 정리한 내용입니다.

05-1 빠른 CPU를 위한 설계 기법

클럭(Clock)

- 컴퓨터 부품들은 ‘클럭 신호’에 맞춰 움직이는데 실제로 클럭 속도가 높은 CPU는 일반적으로 성능이 좋음

- 단위: Hz 로 초당 반복되는 클럭 수

- 실제 CPU 클럭 속도 표현 예시: Base 2.5GHz, Max 4.9GHz 등으로 표시되어있음

- 의미: 초당 25억번, 순간적으로 최대 49억번 반복된다는 의미

오버클럭킹(Overclocking) : 최대 클럭 속도를 강제로 끌어올리는 기법

Q. 클럭 속도를 무지막지하게 높이면 무조건 CPU가 빨라질까?

A. 발열 문제가 심해지고,클럭 속도만으로 cpu의 성능을 올리는 것에는 한계가 있음

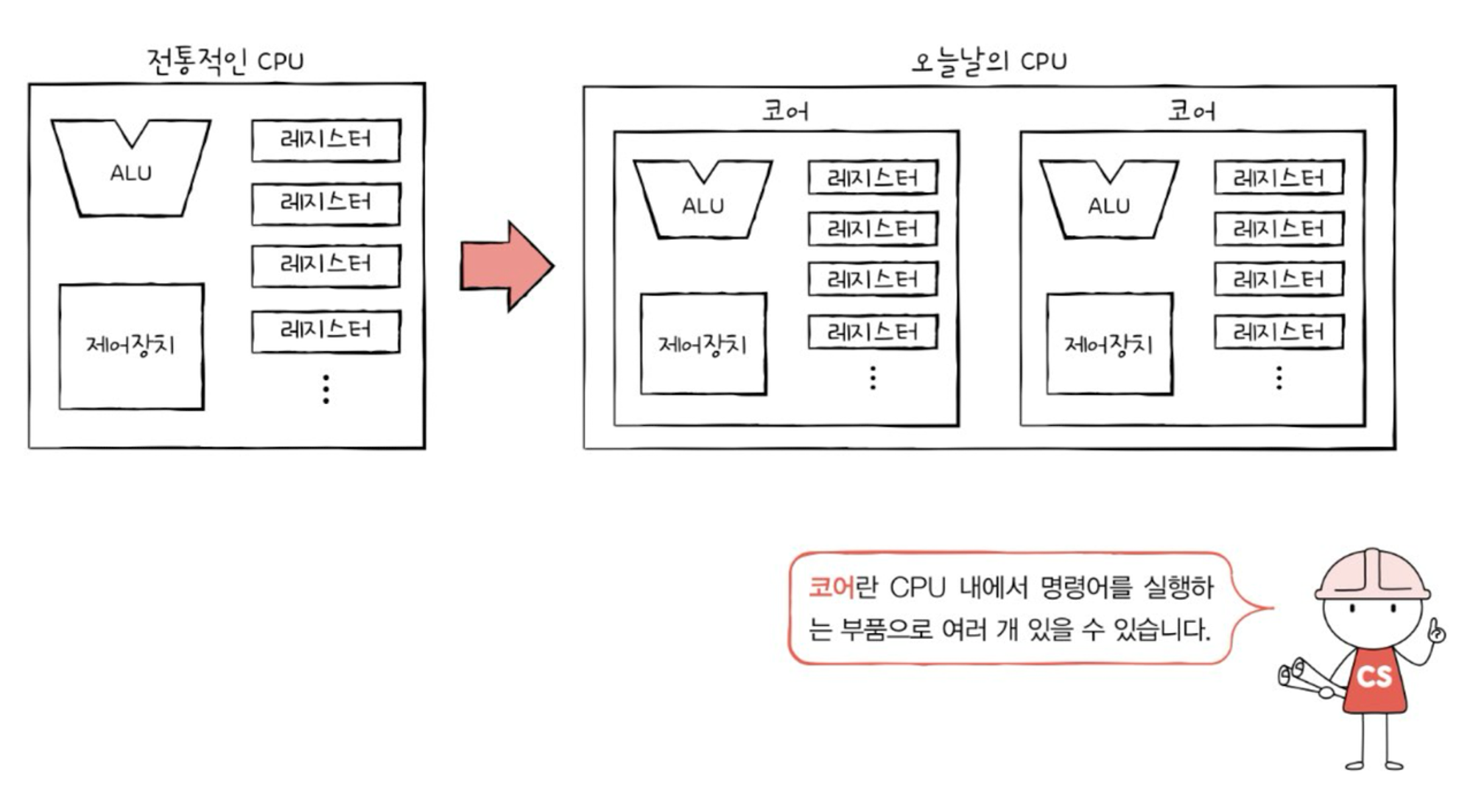

코어와 멀티코어

코어란?

- 명령어를 실행하는 부품으로, CPU가 기술적으로 많은 발전을 거듭하면서 단순히 “명령어를 실행하는 부품” → “명령어를 실행하는 부품을 여러 개 포함하는 부품”으로 확장됨

- 코어를 여러개 포함하고 있는 CPU를 멀티코어 CPU 또는 멀티코어 프로세서라고 부름

- 코어의 개수가 연산 처리 속도와 연관이 있지만 코어마다 처리할 명령어들을 얼마나 적절하게 분배하느냐에 따라 연산 속도가 크게 달라짐

스레드와 멀티스레드

- 스레드: “실행 흐름의 단위”라는 사전적 의미를 가지고 2가지로 나뉨

- 하드웨어적 스레드

- 소프트웨어적 스레드

하드웨어적 스레드

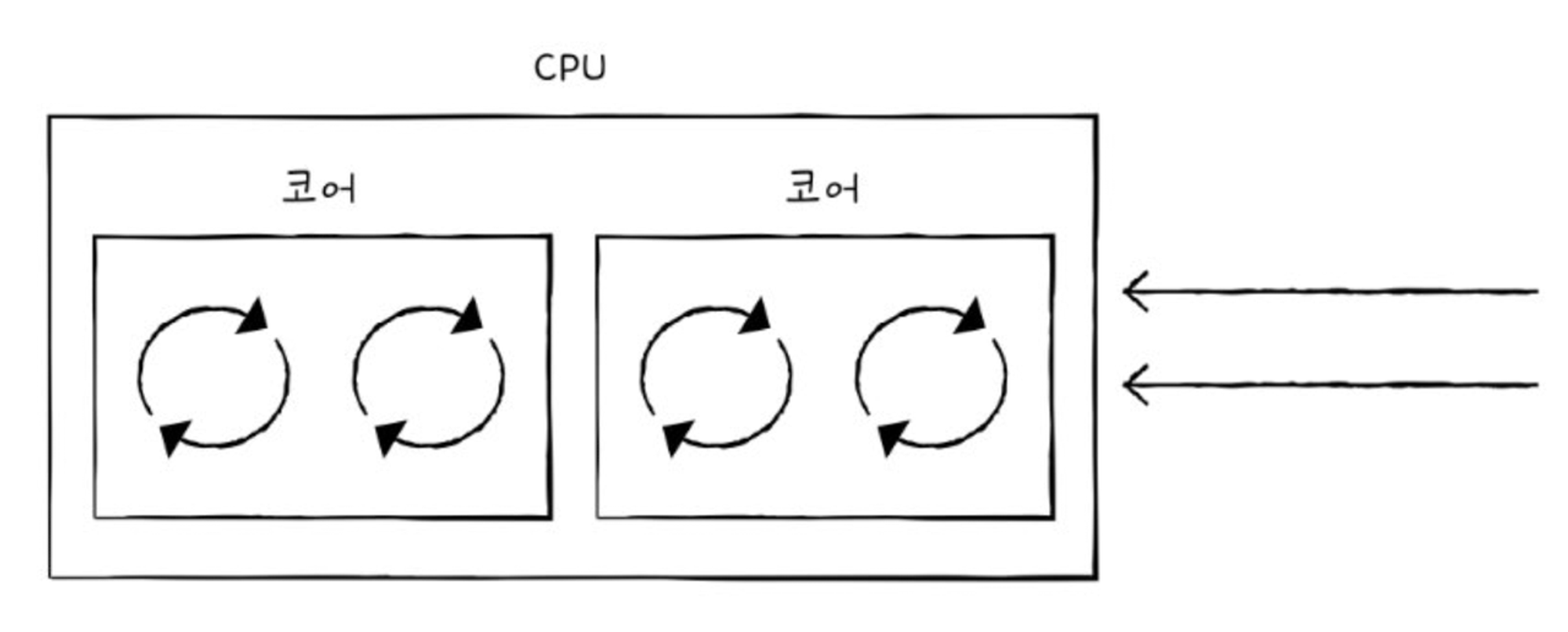

- 하나의 코어가 동시에 처리하는 명령어 단위

- 여러 스레드를 지원하는 CPU는 하나의 코어로도 여러 개의 명령어를 동시에 실행할 수 있음

- 2코어 4스레드 CPU: 아래 그림처럼 명령어를 실행하는 부품 2개, 한번에 4개의 명령어를 처리할 수 있는 CPU를 의미 (멀티스레드 프로세서, 멀티스레드 CPU)

*하이퍼스레딩: 인텔의 멀티스레드 기술을 의미

소프트웨어적 스레드

- 하나의 프로그램에서 독립적으로 실행하는 단위

- 아래의 기능들을 동시에 수행되길 원할 때 각각의 스레드로 만들어 동시 실행할 수 있음

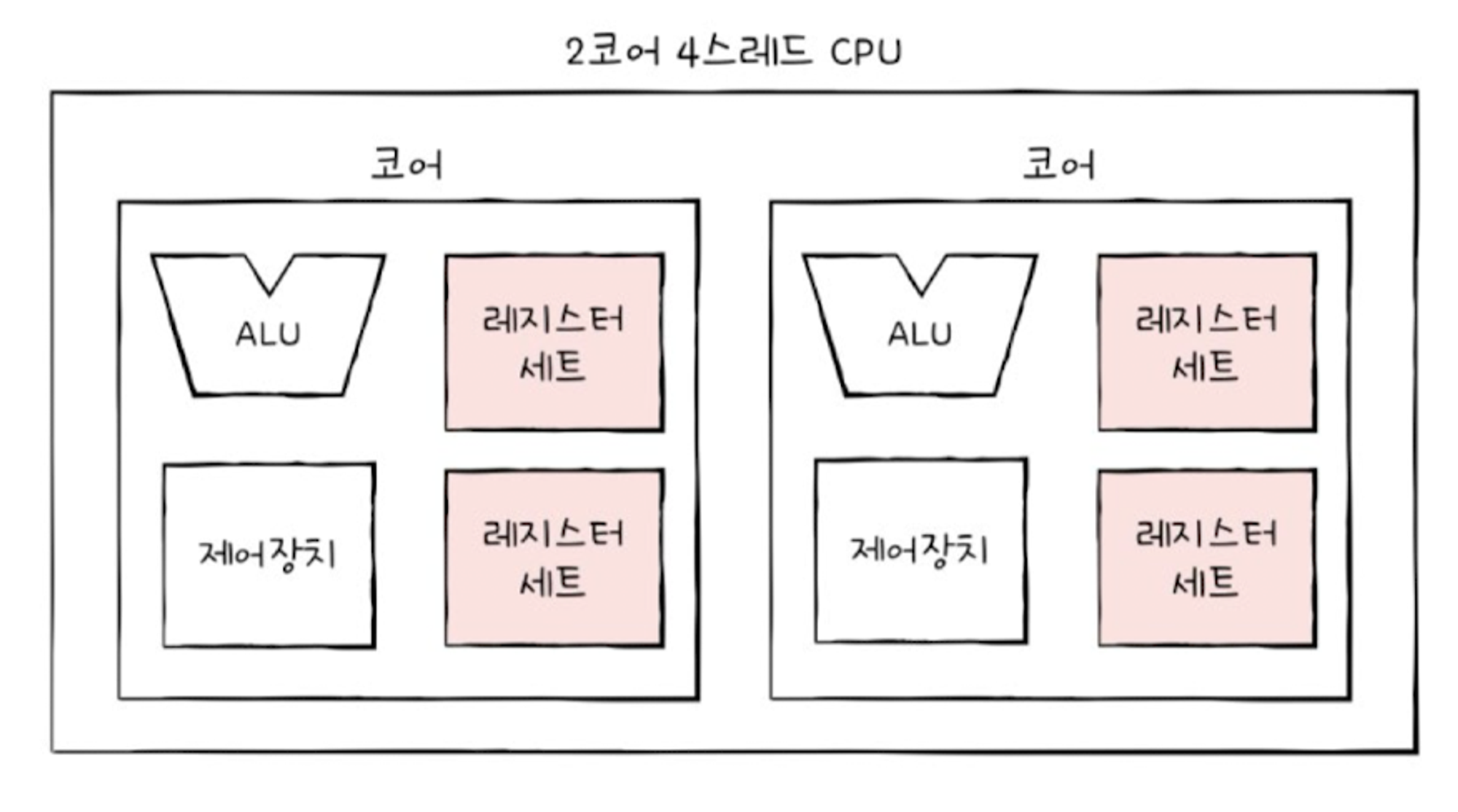

멀티스레드 프로세서

- 하나의 코어로 여러 명령어를 동시에 처리하도록 만들려면 프로그램 카운터, 스택 포인터, 메모리 버퍼 레지스터, 메모리 주소 레지스터와 같이 하나의 명령어를 처리하기 위해 꼭 필요한 레지스터를 여러개 가지고 있으면 됨

- 레지스터세트: 하나의 명령어를 실행하기 위해 꼭 필요한 레지스터들을 편의상 부르기 위한 세트

- 레지스터 세트가 2개인 CPU는 두 개의 명령어를 처리하기 위한 정보들을 기억할 수 있음

- 하드웨어 스레드를 이용해 하나의 코어로도 여러 명령어를 동시에 처리할 수 있다고 했음

- 그러나 메모리 속 프로그램 입장에서는 하드웨어 스레드는 마치 ‘한번에 하나의 명령어를 처리하는 CPU’나 다름 없음 ⇒ 하드웨어 스레드를 논리 프로세서(logical processor)라고 부르기도 함

05-2 명령어 병렬처리 기법

- 빠른 CPU를 만들려면 높은 클럭 속도, 멀티코어, 멀티 쓰레드를 지원하는 CPU를 만드는 것도 중요하지만 CPU가 놀지 않고 시간을 알뜰하게 쓰며 작동하게 만드는 것도 중요

명령어 병렬 처리 기법(ILP: Instruction-Level Parallelism)

- 명령어를 동시에 처리하여 CPU를 한시도 쉬지 않고 작동시키는 기법

- 명령어 파이프 라이닝

- 슈퍼스칼라

- 비순차적 명령어 처리

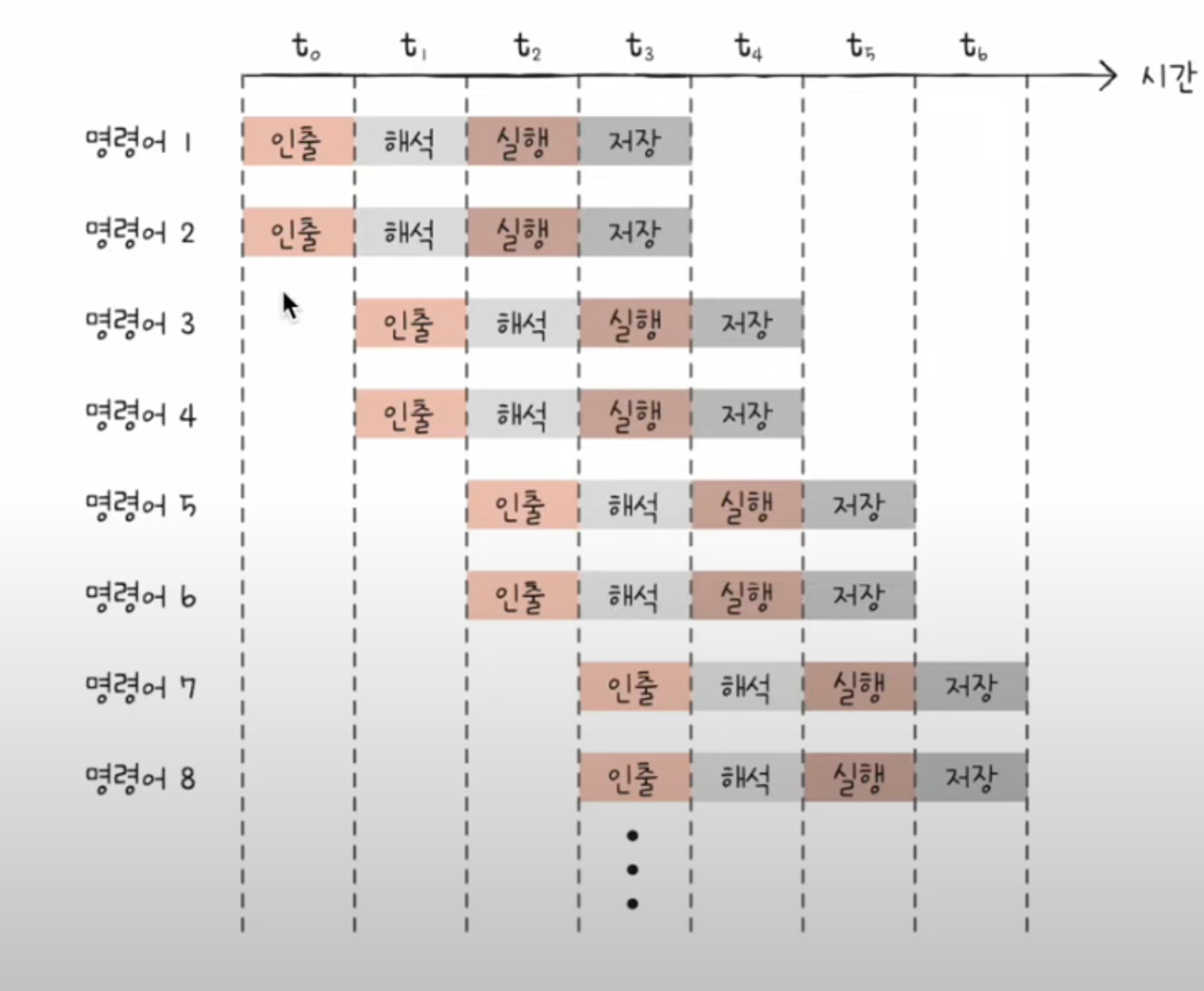

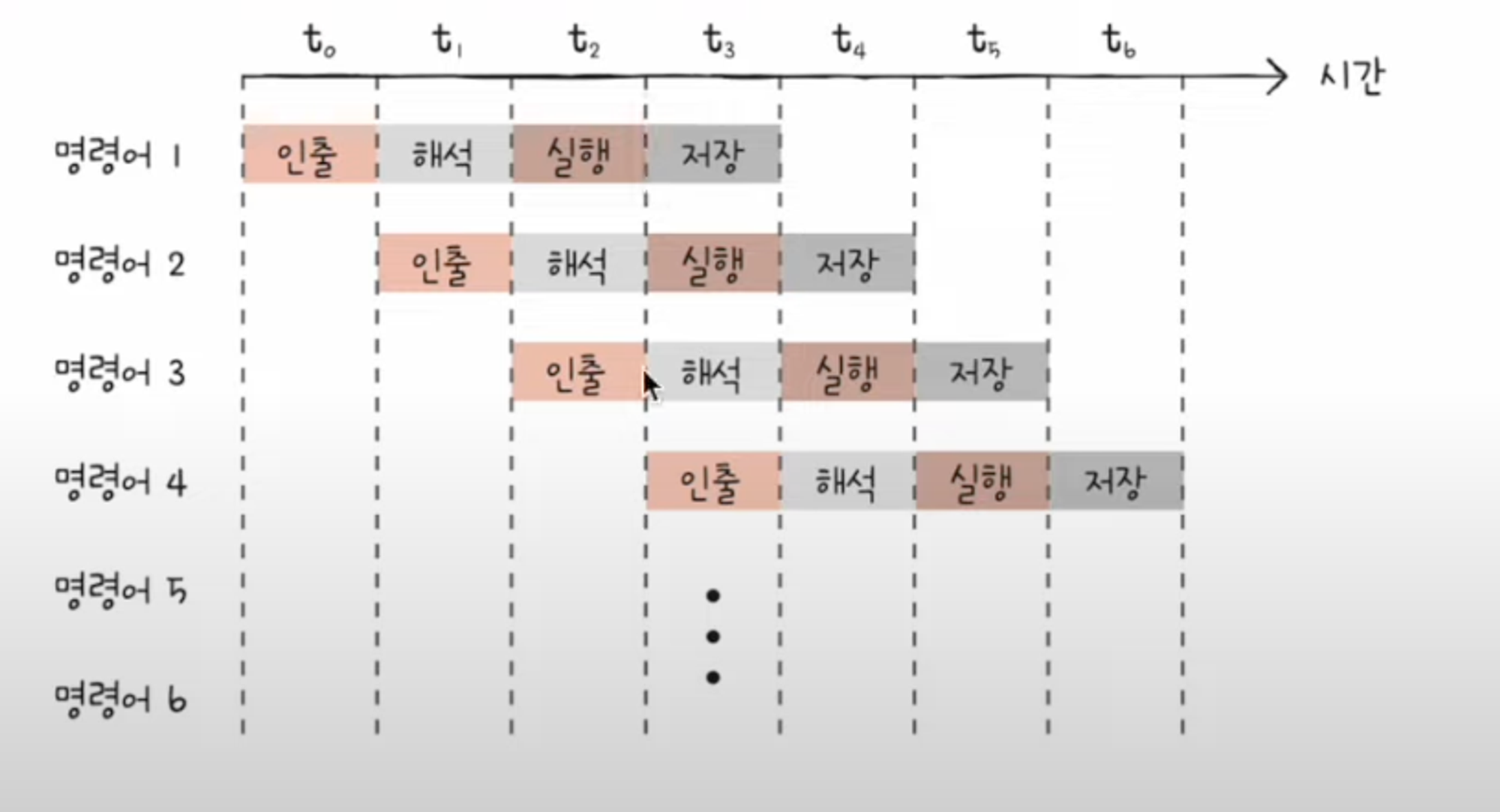

명령어 파이프라인

하나의 명령어가 처리되는 전체 과정을 클럭 단위로 나누면

- 명령어 인출 (Instruction Fetch)

- 명령어 해석 (Instruction Decode)

- 명령어 실행 (Execute Instruction)

- 결과 저장 (Write Back)

같은 단계가 겹치지만 않는다면 CPU는 ‘각 단계를 동시에 실행할 수 있다’

⇒ 명령어 파이프라인에 넣고 동시에 처리하는 기법을 명령어 파이프라이닝이라고 함

명령어 파이프라인을 사용하지 않고 모든 명령어를 순차적으로만 처리하면 아래와 같이 비효율적으로 처리됨

파이프라이닝이 높은 성능을 가져오기는 하지만, 성능 향상에 실패하는 경우도 있음 → 파이프라인 위험

파이프라인 위험 3가지 종류

- 데이터 위험 (Data hazard)

- 제어 위험 (Control hazard)

- 구조적 위험

데이터 위험

- 명령어 간의 의존성때문에 발생하는 위험

- 모든 명령어를 동시에 처리할 수 없는 경우도 있기 때문

명령어 1: R1 <- R2 + R3

명령어 2: R4 <- R1 + R5

명령어 1을 실행 후에 명령어 2에서 명령어 1의 결과를 인출해야 하기때문에 병렬적으로 처리할 수 없음

제어 위험

- 기본적으로 프로그램 카운터는 ‘현재 실행 중인 명령어의 다음 주소’로 갱신됨

- 분기 등으로 인한 프로그램 카운터의 갑작스러운 변화가 생기면 명령어 파이프라인에 가지고 와서 처리 중(ex) 인출, 해석)이던 명령어들이 쓸모 없어짐

⇒ 분기 예측을 통해 프로그램이 어디로 분기할지 미리 예측한 후 그 주소를 인출하는 기술을 사용

구조적 위험

- 명령어들을 겹쳐 실행하는 과정에서 서로 다른 명령어가 동시에 ALU, 레지스터 등과 같은 CPU 부품을 사용하려고 할 때 발생 ⇒ 자원 위험이라고도 부름

슈퍼스칼라

- 여러개의 파이프라인을 이용해서 한번에 두가지의 명령어를 인출/해석/실행/저장

- 이론적으로는 파이프라인 개수에 비례하여 처리속도 증가, but 파이프라인 위험도 증가하기 때문에 고도로 설계 되어야 함

비순차적 명령어 처리

- OoOE: Out-of-order execution

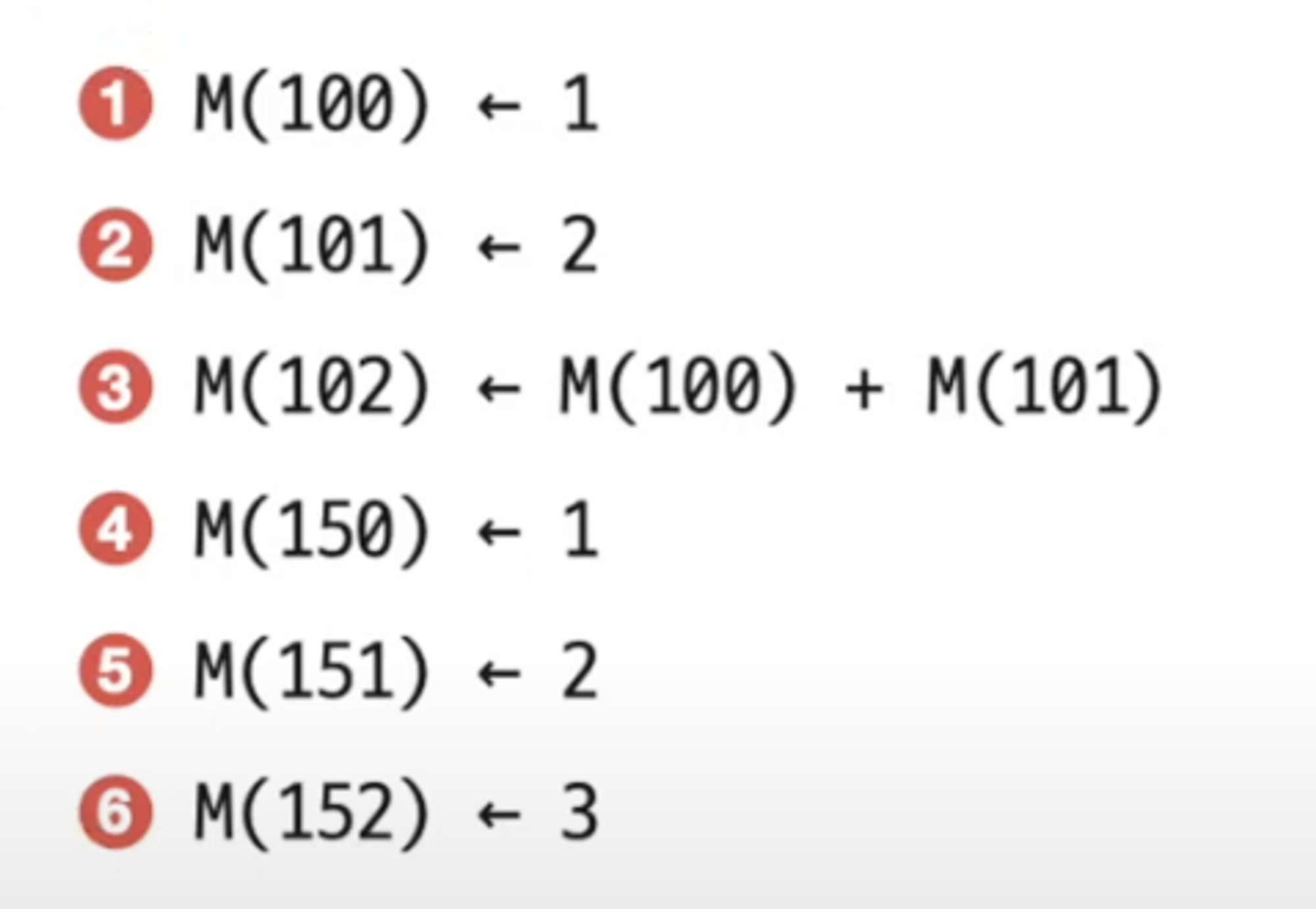

- M(N): N 번지의 메모리

- M(N) ← 100: N 번지에 100을 저장

3번째 명령어 (M(102) <- M(100) + M(101)) 에서 1, 2번째 명령어의 결과가 필요하기 때문에 이상적인 성능 향상을 이끌 수 없음

여기서 의존성이 없는 명령어의 순서를 바꿔본다면?

- 순차적으로 명령어를 처리할 때 보다 더 효율적으로 처리될 수 있고 이렇게 명령어 파이프라인을 멈추는 것을 방지하는 기법을 비순차적 명령어 처리 기법이라고 함

* 물론 아무 명령어나 순서를 바꿔서 수행할 수는 없고 최적화 필요

05-3 CISC 와 RISC

- CPU 성능을 향상시키기 위해서 명령어 파이프라이닝, 슈퍼 스칼라 기법등을 적용하기 위해서는 명령어가 파이프라이닝 하기 쉽게 생겨야 함

CPU는 명령어를 실행한다 ⇒ 모든 CPU가 똑같이 생긴 명령어를 실행할까? NO!

명령어의 세세한 생김새, 연산, 주소 지정 방식은 CPU마다 다름

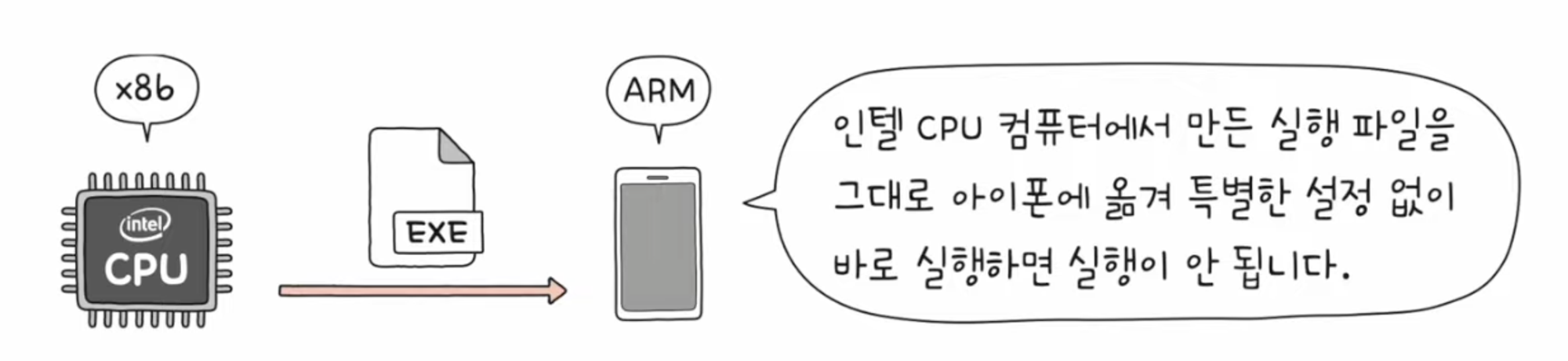

명령어 집합 (Instruction set, Instruction set architecture, ISA)

- CPU가 이해할 수 있는 명령어들의 모음

- 인텔의 CPU가 이해할 수 있는 명령어 집합과 아이폰의 CPU가 이해할 수 있는 명령어 집합은 다름

명령어 병렬 처리 기법들을 도입하기 유리한 ISA는 크게 2가지가 있음

- CISC

- RISC

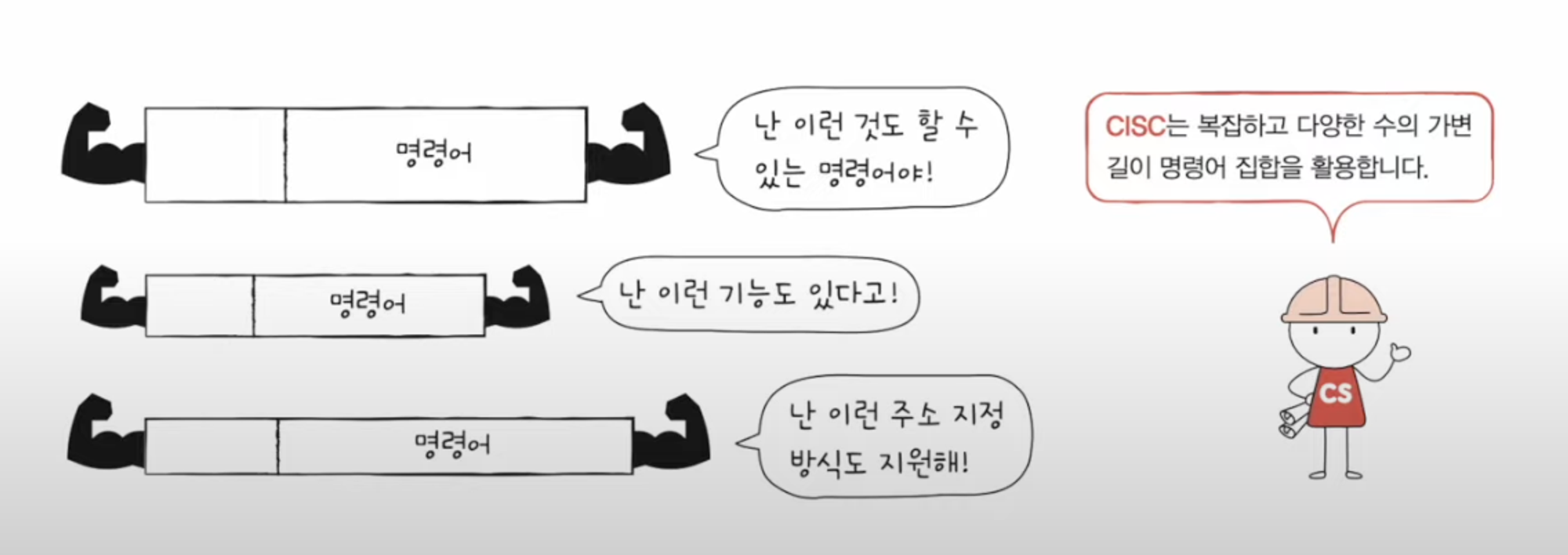

CISC

- Complex Instruction Set Computer

- 복잡한 명령어 집합을 활용하는 컴퓨터(CPU)

- Intel, AMD 기반 cpu (x64, x86-64)

- 복잡하고 다양한 명령어 활용

- 명령어의 형태와 크기가 다양한 가변 길이 명령어 활용

- 상대적으로 적은 수의 명령어로도 프로그램을 실행할 수 있음 ⇒메모리를 최대한 아끼며 개발해야했던 시절에 인기가 높았음

- 명령어 파이프라이닝이 불리하다는 치명적인 단점이 있음

- 명령어가 워낙 복잡하고 다양한 기능을 제공해 명령어의 크기와 실행되기까지의 시간이 일정하지 않음

- 명령어 실행하는데 여러 클럭 주기 필요

⇒ CISC 명령어 집합은 복잡하고 다양한 기능을 제공하기에 적은 수의 명령어로 프로그램을 동작시키고 메모리를 절약할 수 있지만, 명령어의 규격화가 어려워 파이프라이닝이 어려움

RISC

- Reduced Instruction Set Computer

- 명령어의 종류가 적고, 짧고 규격화된 명령어 사용 (되도록 1클럭 내외로 실행되는 명령어를 지향) ⇒ 고정 길이 명령어 사용

- 메모리에 직접 접근 명령어를 load, store 두개로 제한할 만큼 메모리 접근을 단순화 및 최소화

- 레지스터를 십분 활용 → 범용 레지스터 수가 더 많음

- 다만 명령어 종류가 CISC 보다 적기에 더 많은 명령어로 프로그램을 동작시킴

참고

1. 책 "혼자 공부하는 컴퓨터 구조+운영체제"

2. 유튜브 "혼자 공부하는 컴퓨터 구조 + 운영체제"